计算机组成原理 期末复习

第 1 章 计算机系统概论

1.1 计算机的诞生和发展

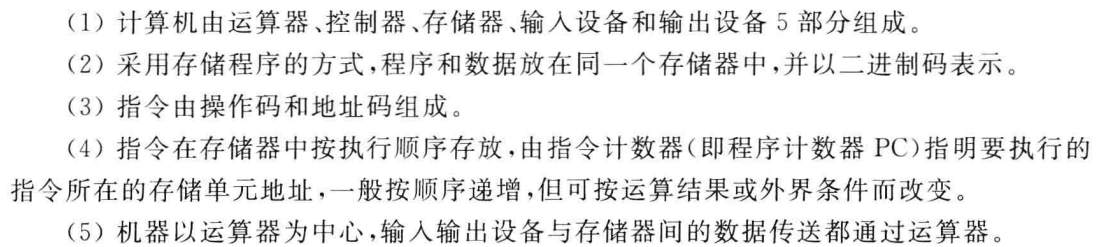

冯诺依曼体系

1.2 计算机的硬件

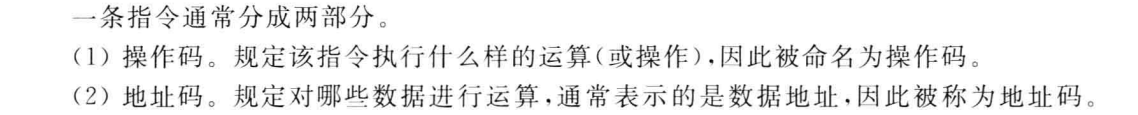

指令

硬件组成

组成计算机的基本部件有中央处理器(CPU,运算器和控制器)、存储器和输入输出设备。

计算机系统分类

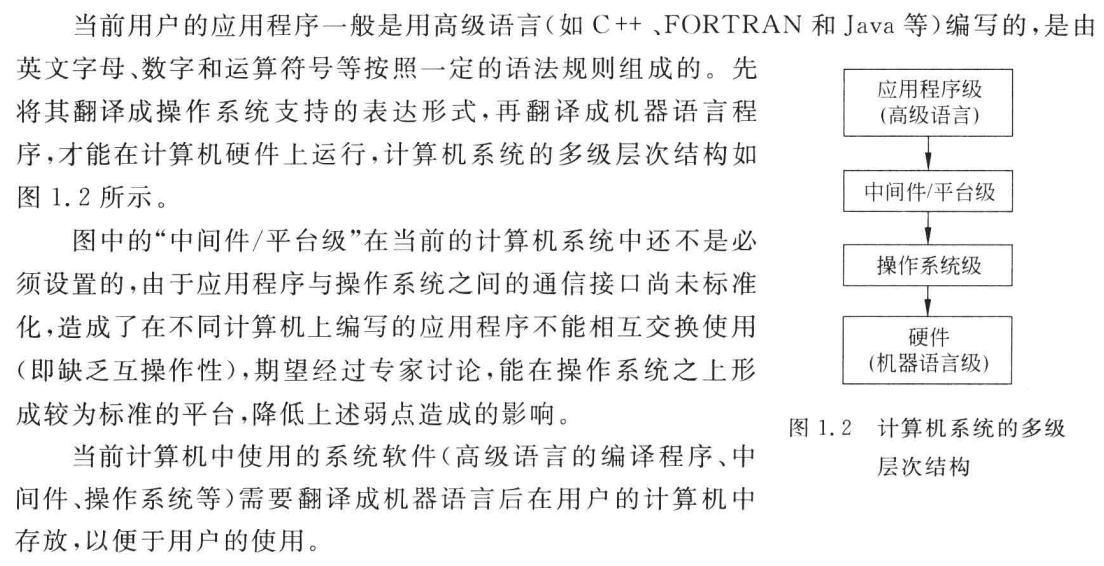

1.2 计算机的软件

机器语言 汇编语言 高级语言

操作系统

第 2 章 计算机的逻辑部件

2.1 组合逻辑电路

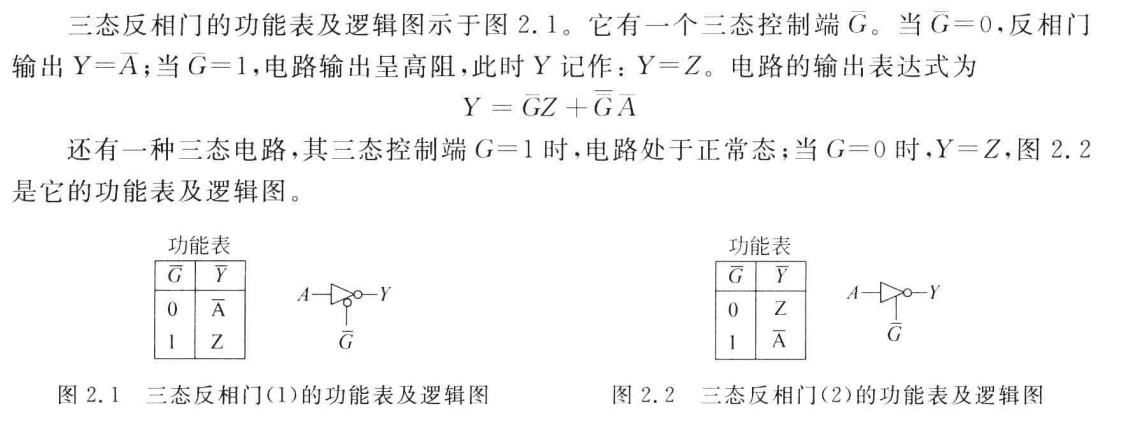

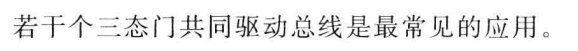

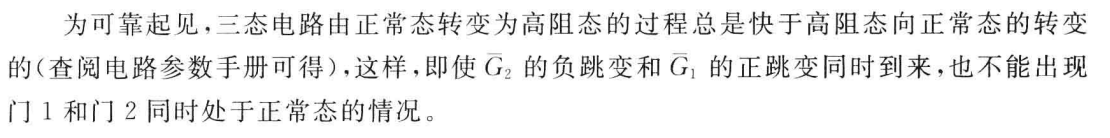

三态电路

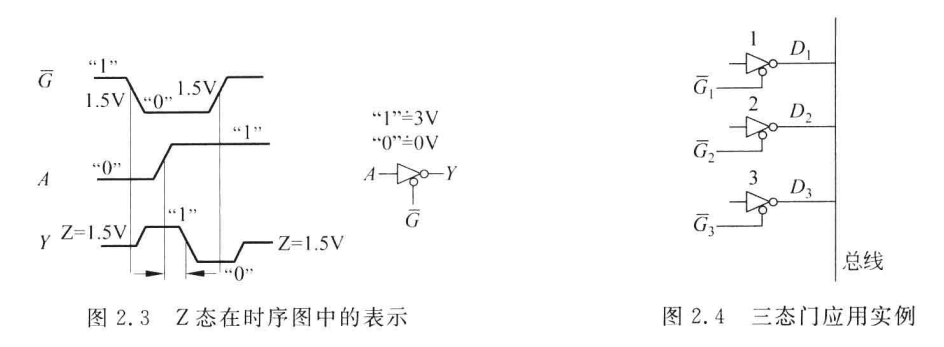

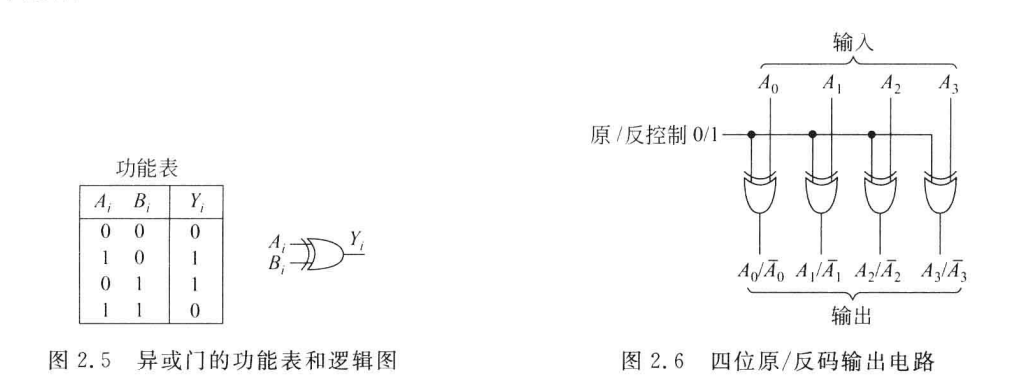

异或门的应用

(1)原码/反码输出电路

(2)半加器

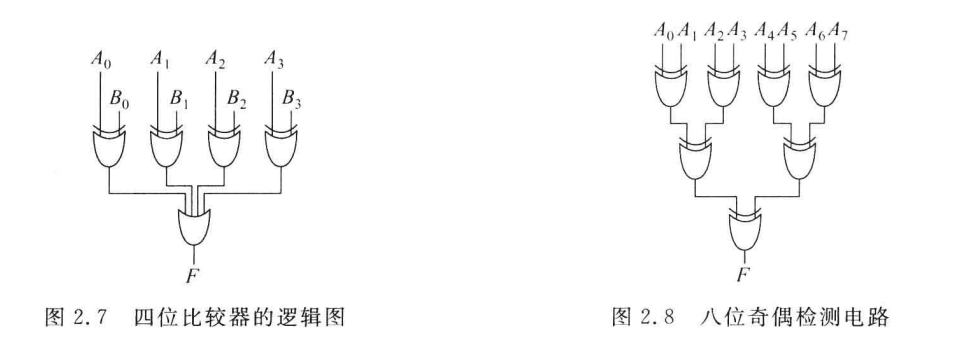

(3)数码比较器

(4)奇偶检测电路

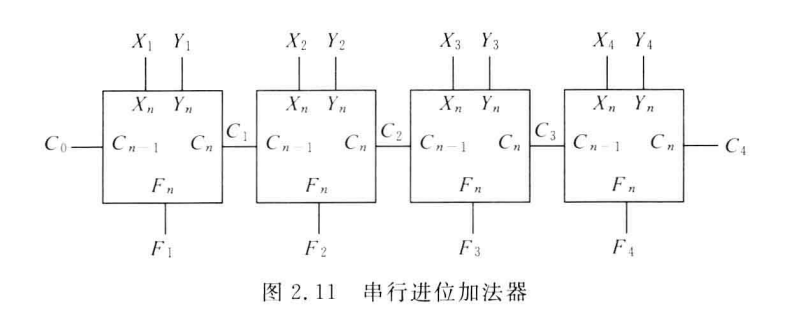

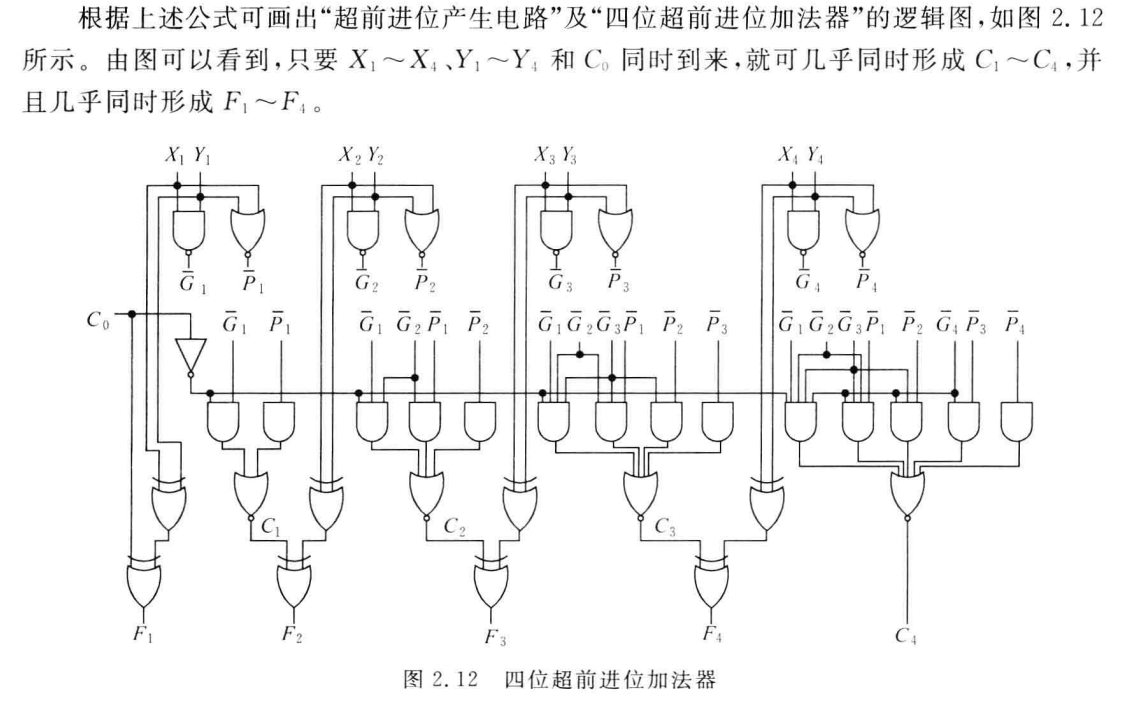

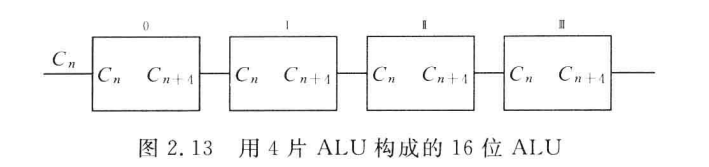

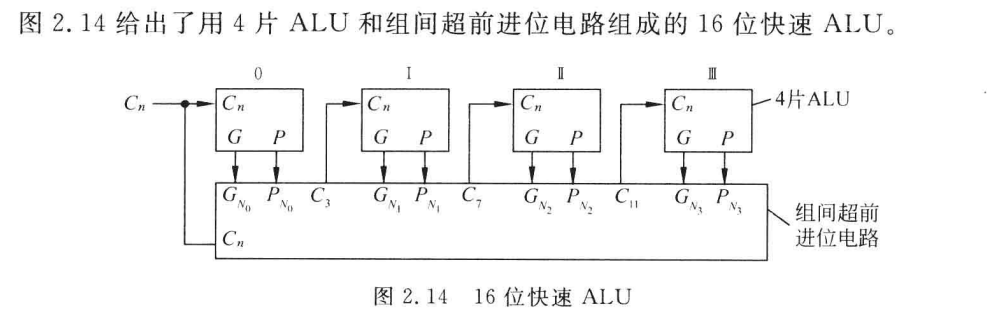

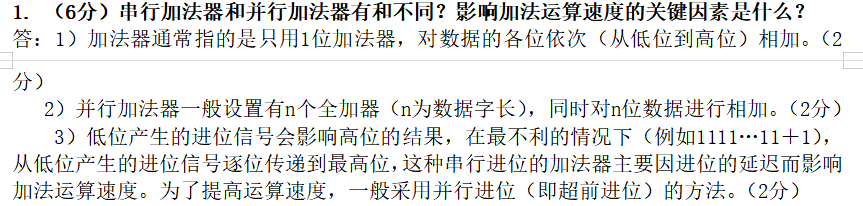

加法器

题:加法器

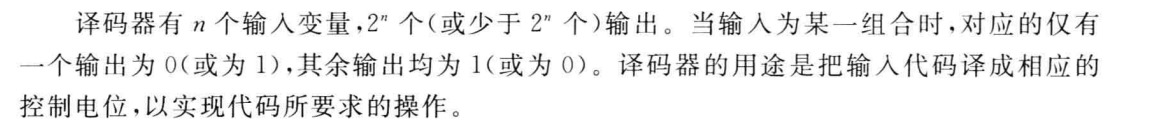

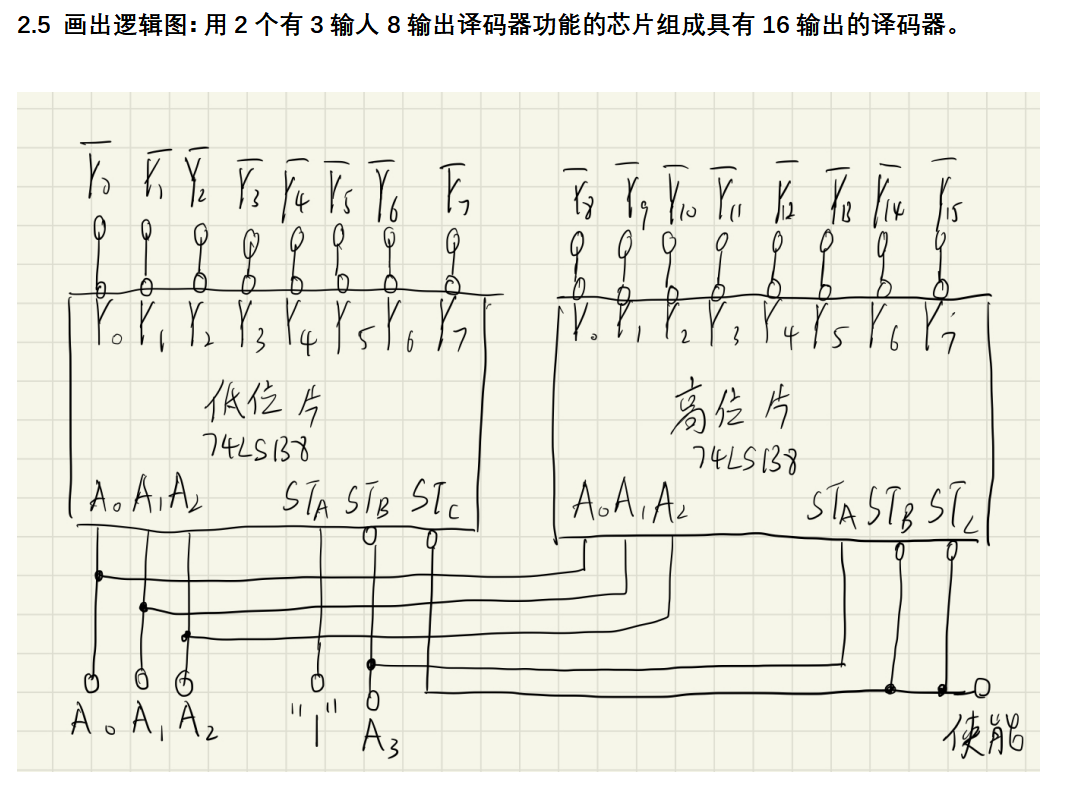

译码器

数据选择器

2.2 时序逻辑电路

触发器

电位触发器 锁存器 可以组成暂存器

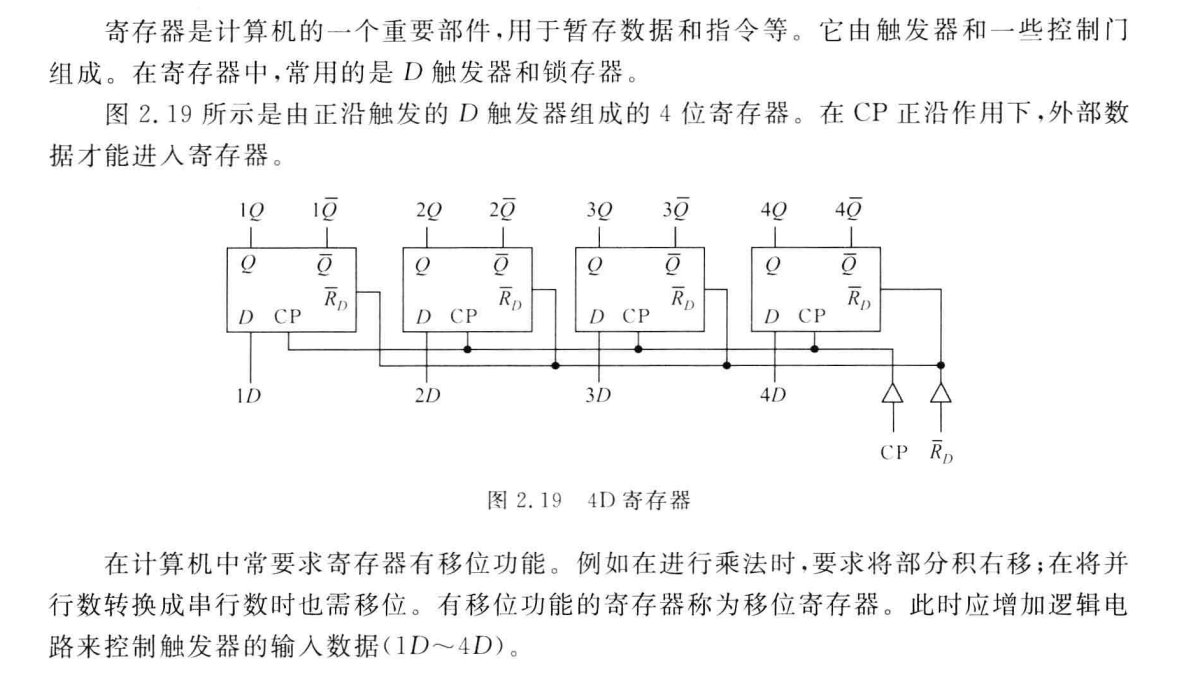

边沿触发器 D触发器 可以组成寄存器、计数器、移位寄存器

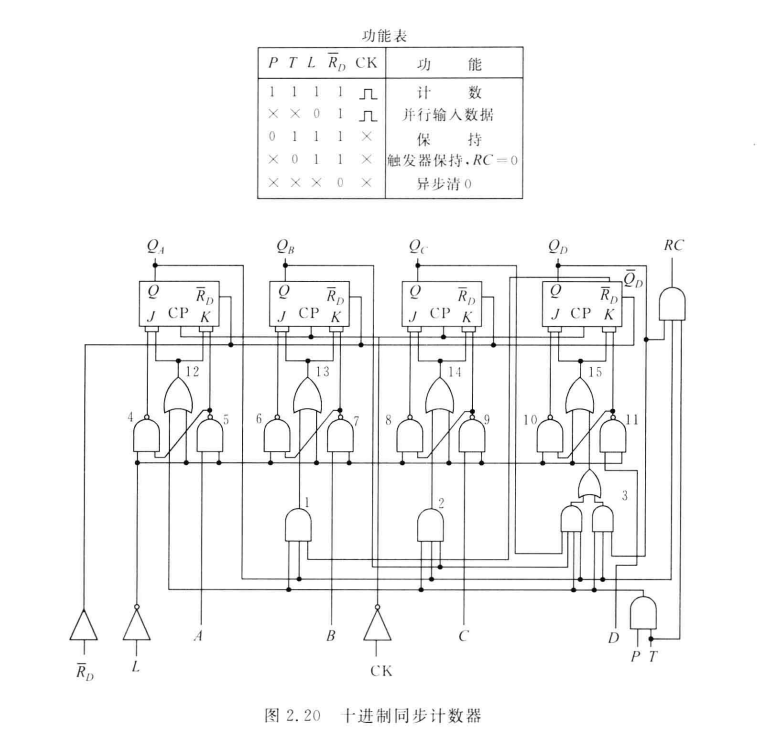

主从触发器 JK触发器 可以组成计数器

寄存器 移位寄存器

计数器

2.3 阵列逻辑电路

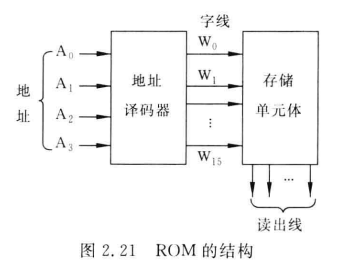

只读存储器 ROM

用于存储固定信息,如监控程序、函数和常数

由地址译码器(与阵列)和存储单元(或阵列)构成

可编程序逻辑阵列 PLA

由与阵列、或阵列组成,都可编程

采用熔丝工艺

可编程序阵列逻辑 PAL

与阵列可编程,或阵列不可编程

采用熔丝工艺

通用阵列逻辑 GAL

门阵列 GA 宏单元阵列 MCA

现场可编程门阵列 FPGA

第 3 章 运算方法和运算部件

3.1 数据的表示方法和转换

进制转换

N转十:位值原理

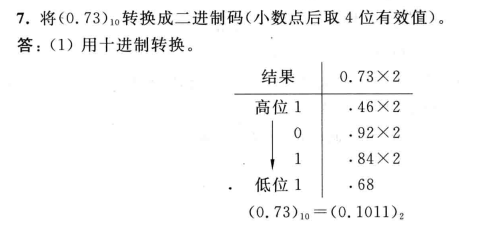

十转N:整数部分,短除法(除N取余);小数部分,乘N取整

十进制可以精确表示二进制,二进制不能精确表示十进制

题:进制转换

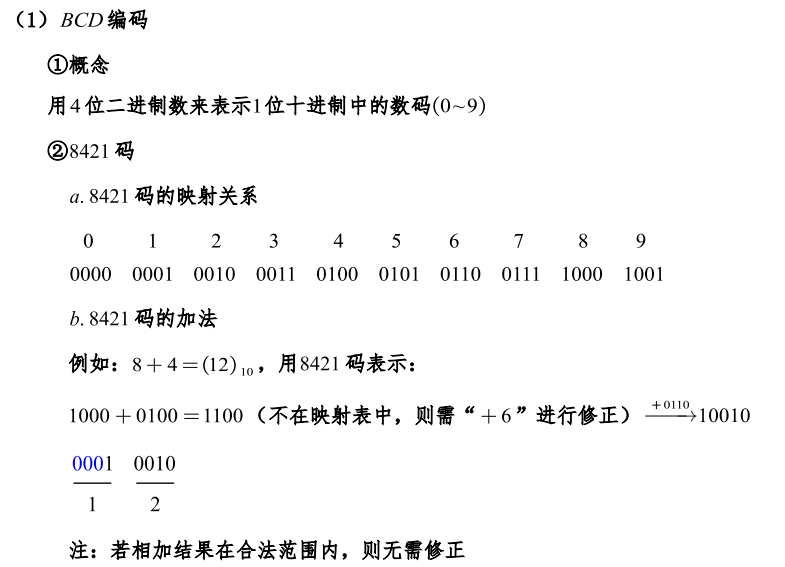

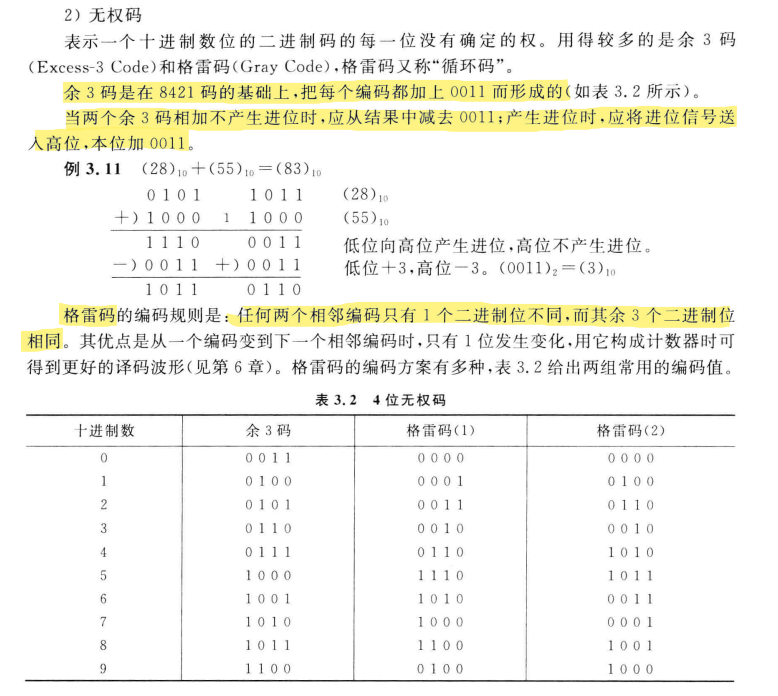

编码

3.2 数据表示和加减法

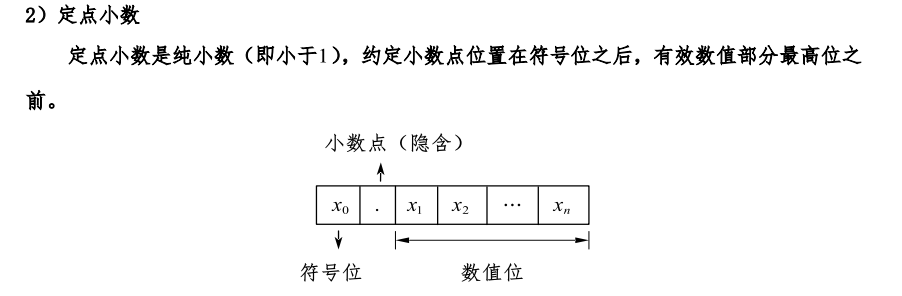

数据表示

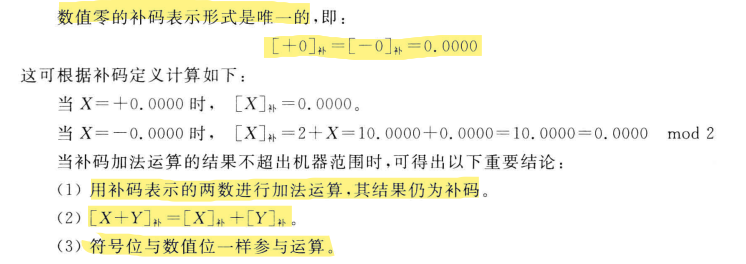

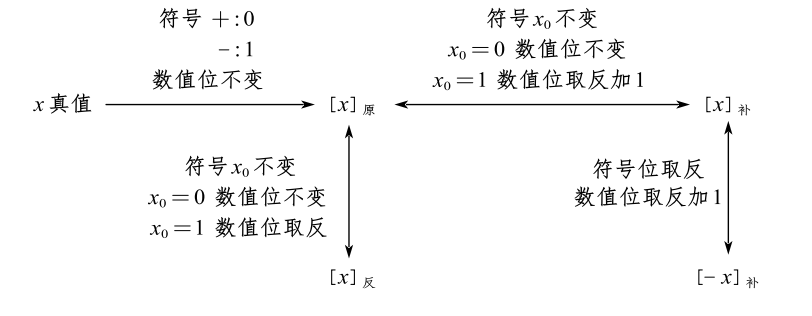

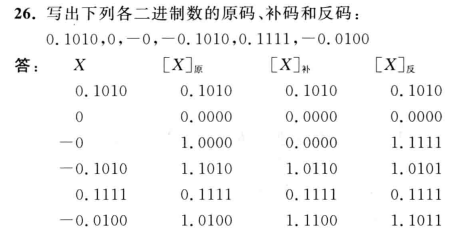

题:数据表示

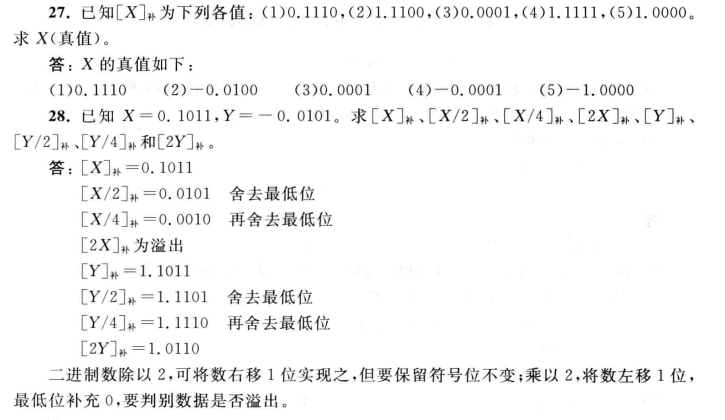

补码右移时要计入符号位,即移动符号位的值,但是符号位本身保持不变。左移时,如果符号位改变,则发生溢出。

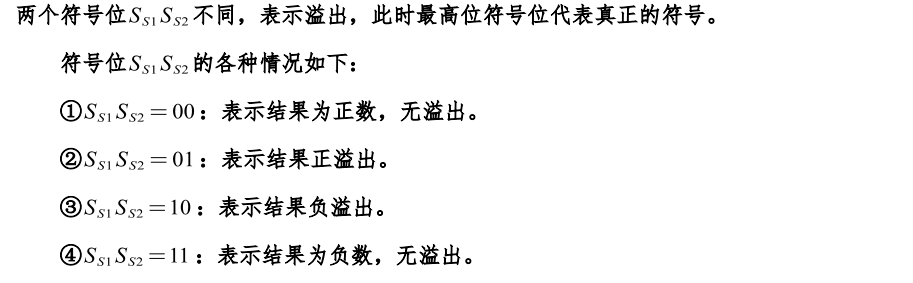

溢出检查

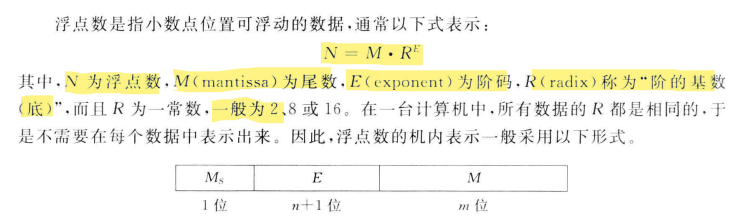

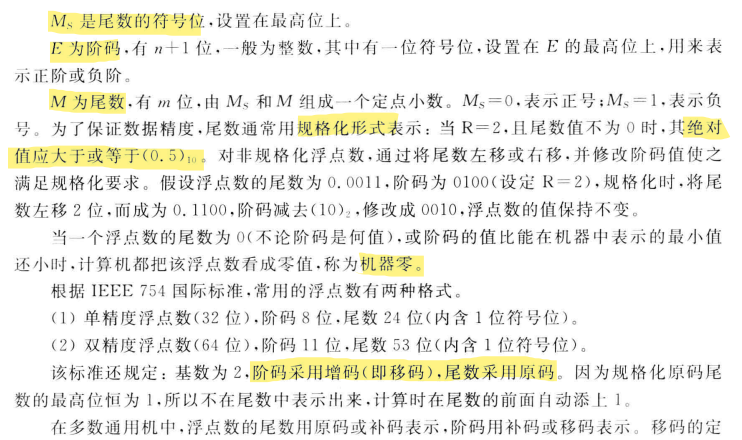

浮点数

规格化就是尾数除了符号位之外的最高位一定为1

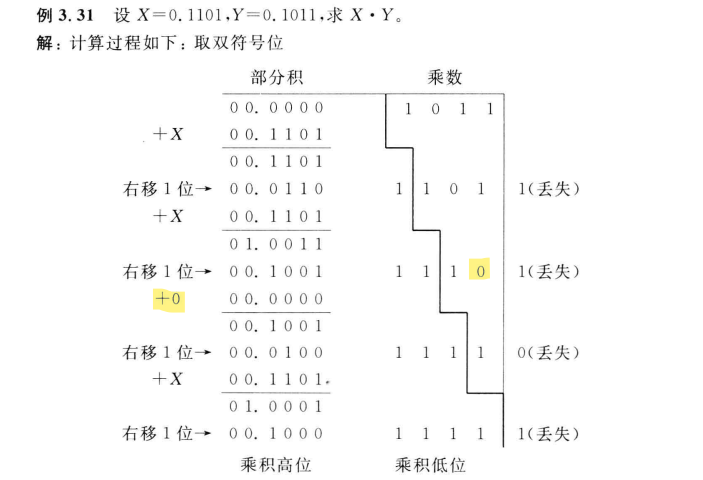

3.3 二进制乘法

原码一位乘

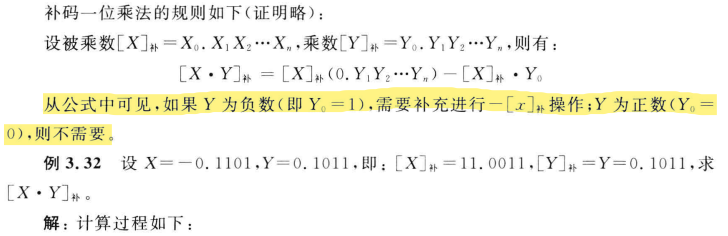

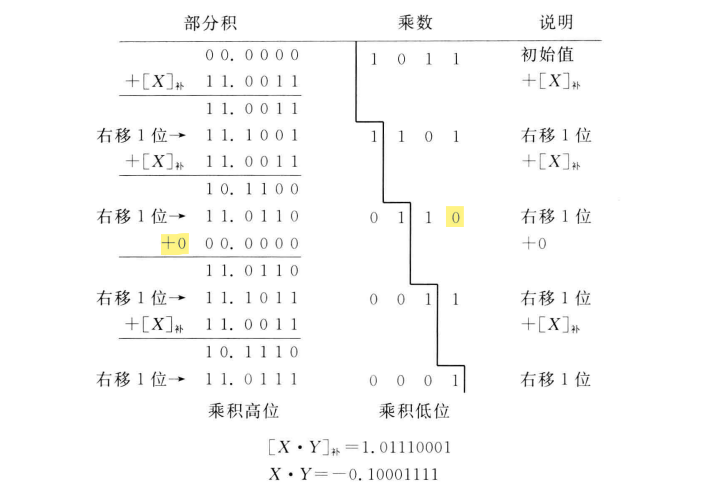

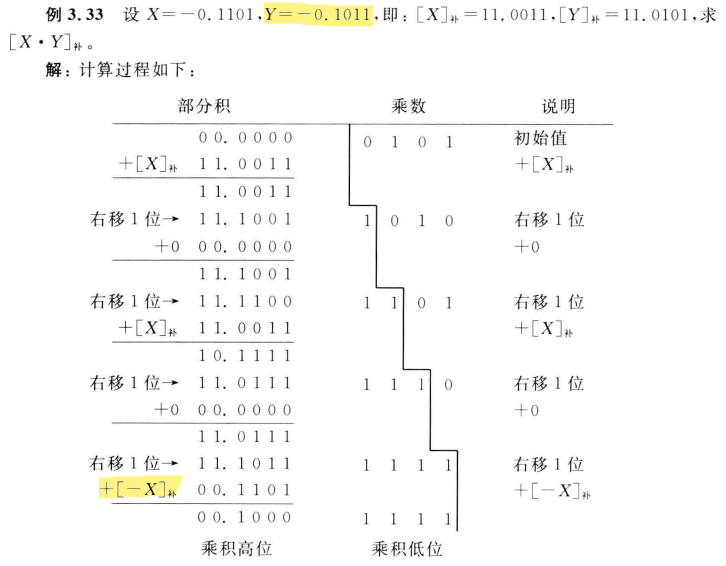

补码一位乘

补码的X符号位加入运算

若Y<0,最后加[-X]补

补码一位乘:布斯公式

布斯法,Y的符号位也参加运算,单符号位,Y最后补0(Y左右两边都要补数字)

部分积 + [(Y_(i+1)-Y_i*X]补

注意,不需要全部右移完毕,在下题中右移4次就结束。

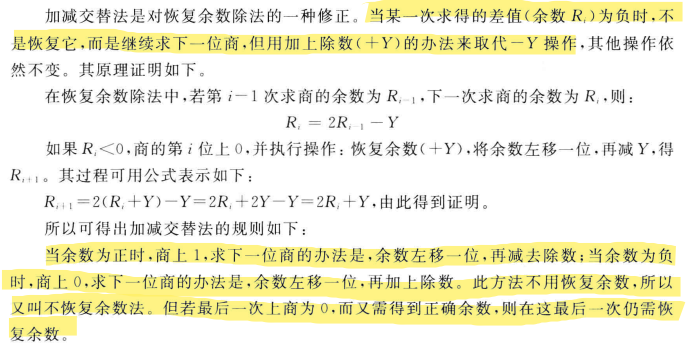

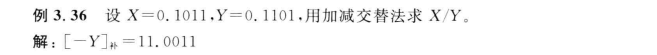

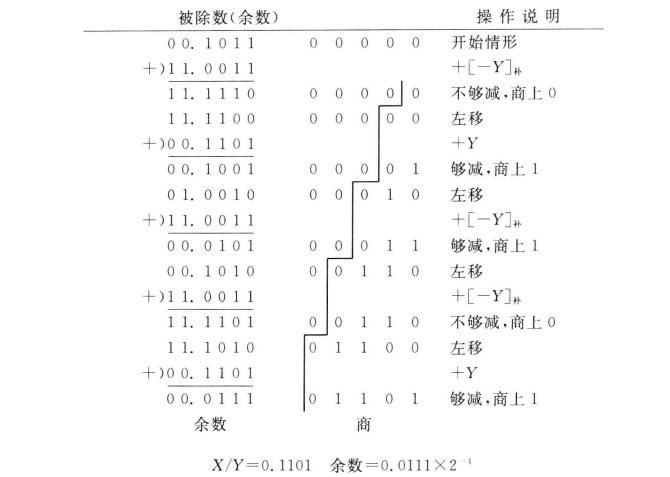

3.4 二进制除法

原码一位除:加减交替法

商带符号位,多一位

3.5 浮点数运算

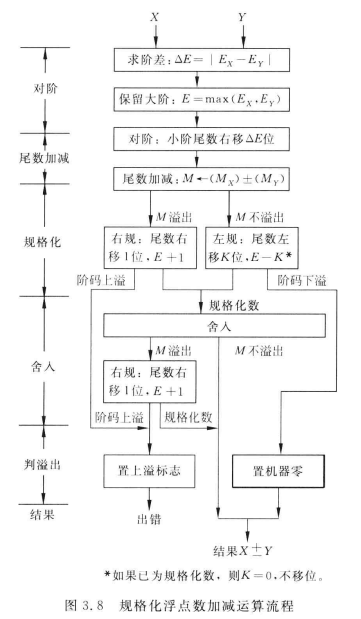

浮点数加减法

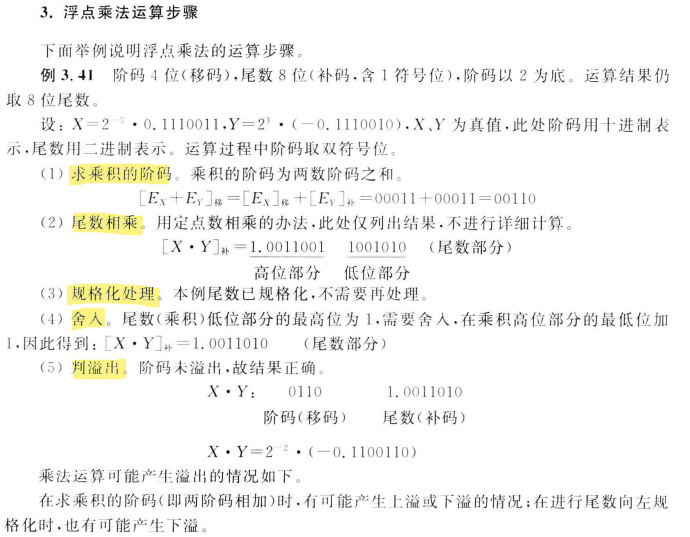

浮点数乘除法

3.7 数据校验码

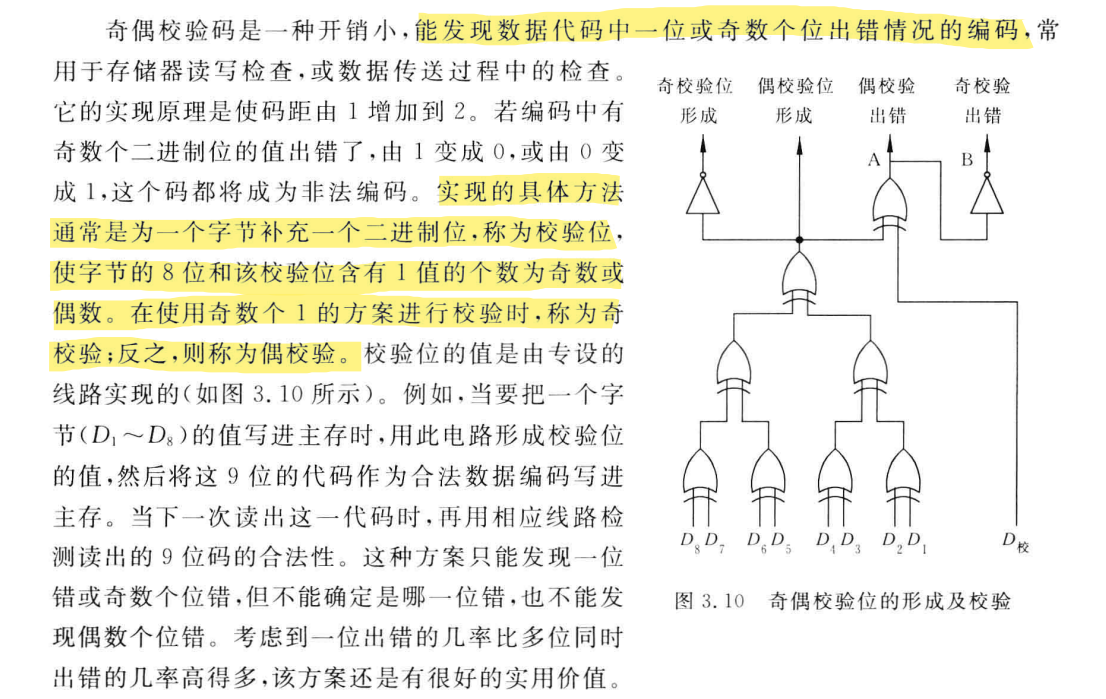

奇偶校验码

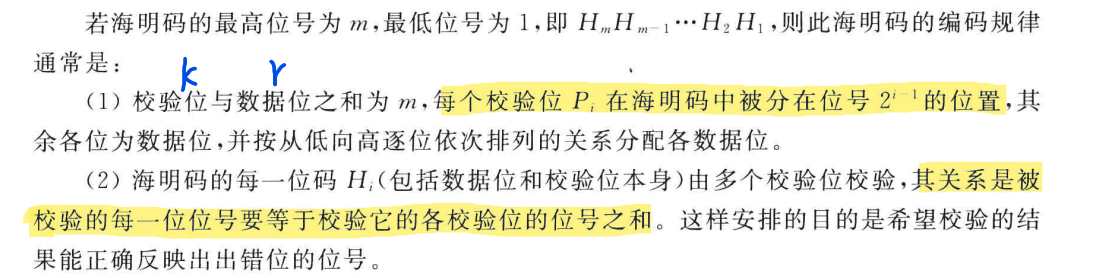

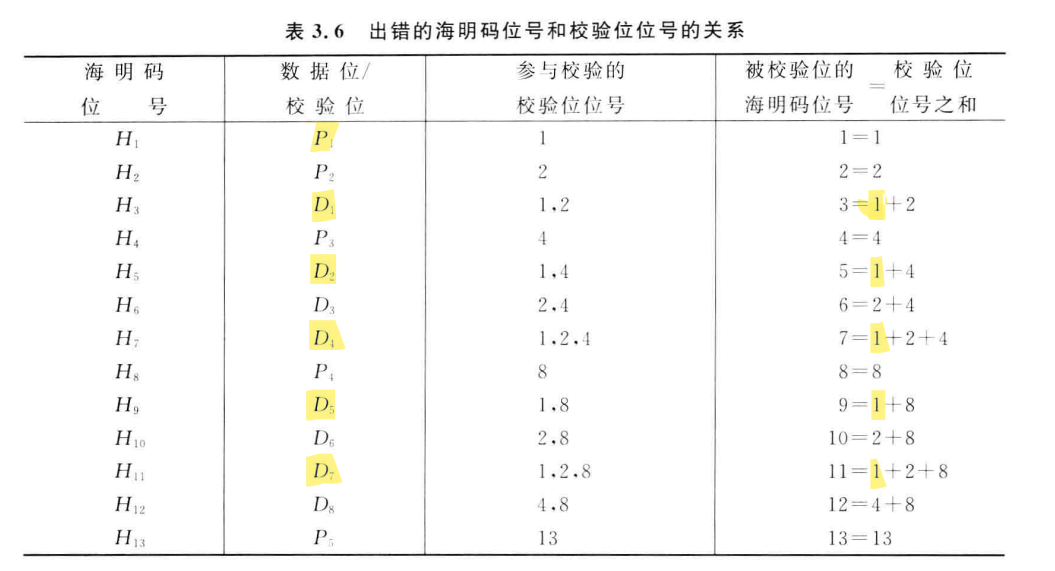

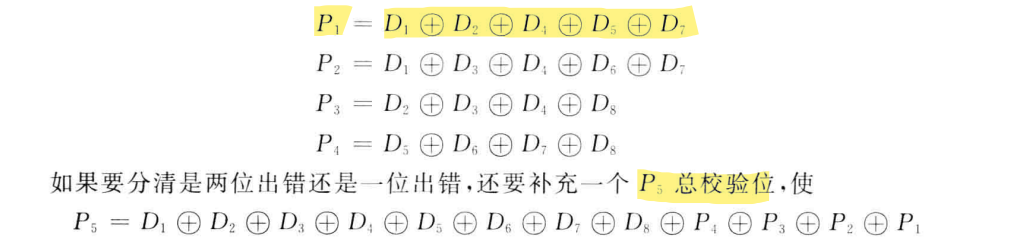

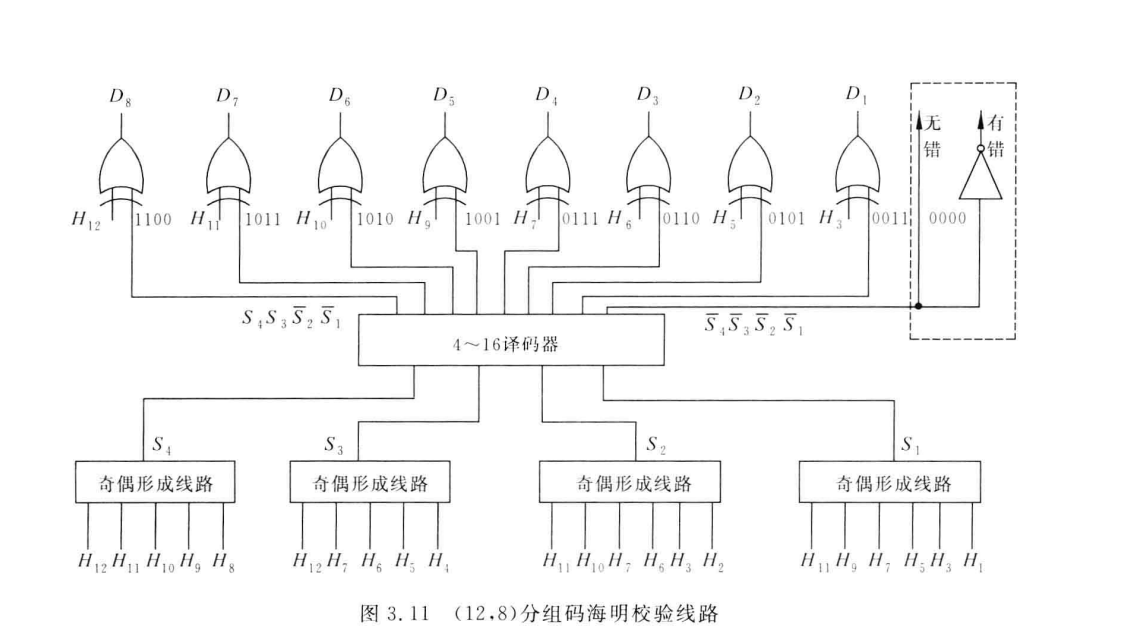

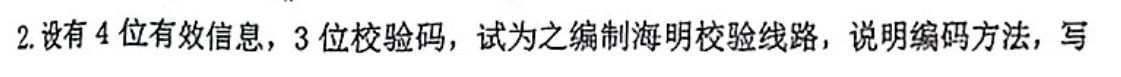

海明码

题:海明码

第 4 章 主存储器

4.1 主存储器分类、技术指标和基本操作

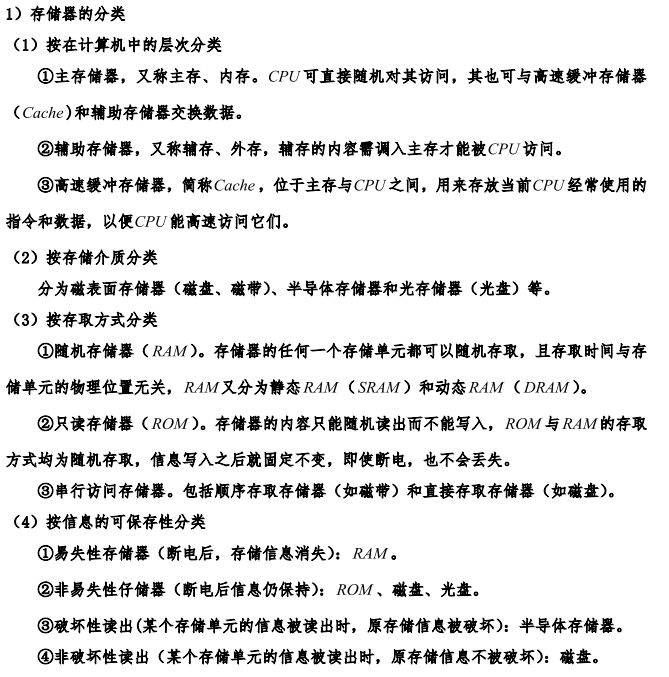

存储器的分类

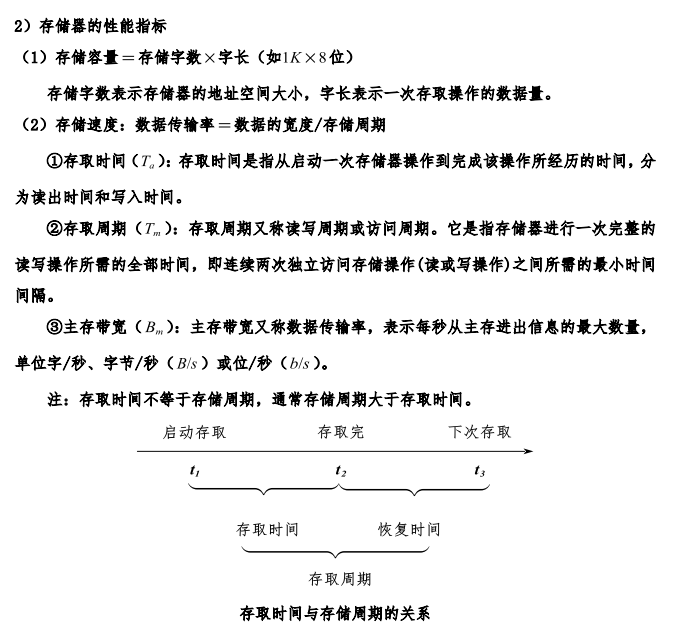

主存储器的技术指标

4.2 读/写存储器

都是易失性存储器,断电丢数据

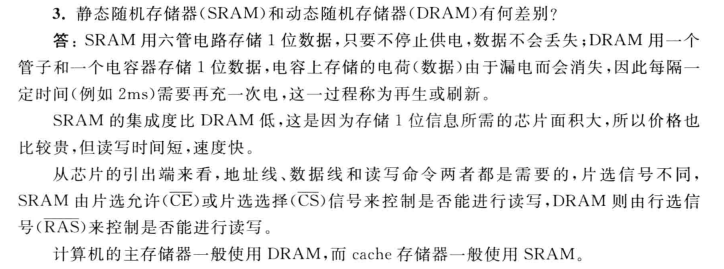

SRAM 速度快,体积大,功率大

DRAM 便宜,容量大

静态随机存储器 SRAM

双稳态触发器

动态随机存储器 DRAM

4.3 非易失性半导体存储器

只读存储器 ROM

可编程 只读存储器 PROM

熔丝,一次性编程

可擦可编程 只读存储器 EPROM

编程次数不受限制,电写,紫外线擦除

可电擦可编程序 只读存储器 E^2PROM

电擦,电写,次数10万次

快擦除读写存储器 Flash Memory

即闪存

4.4 容量扩展

位扩展

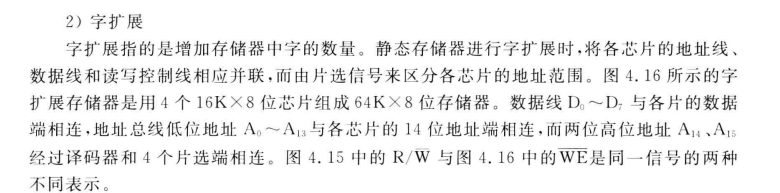

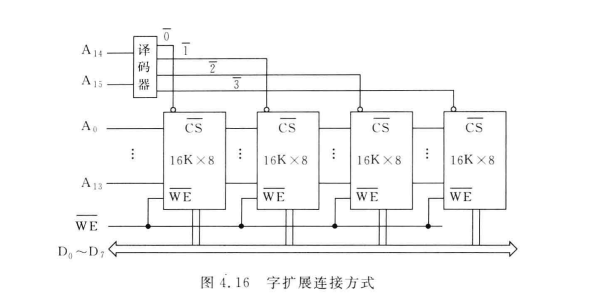

字扩展

字位同时扩展

第 5 章 指令系统

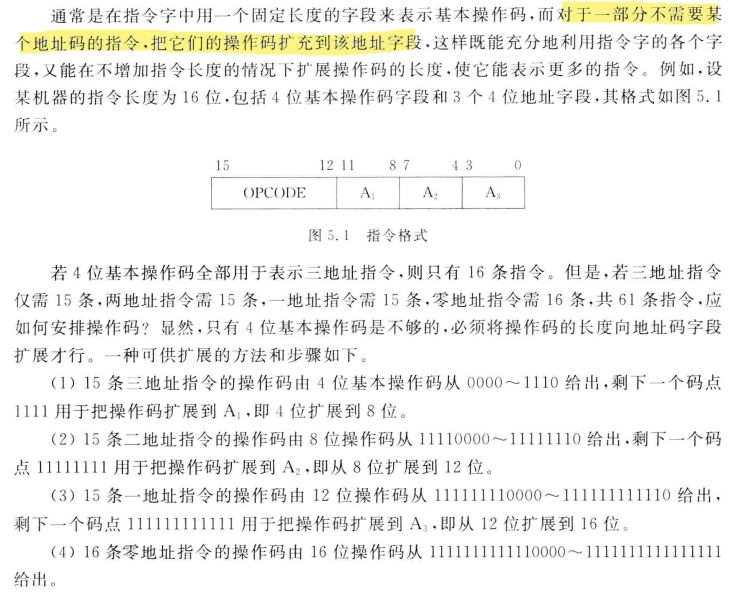

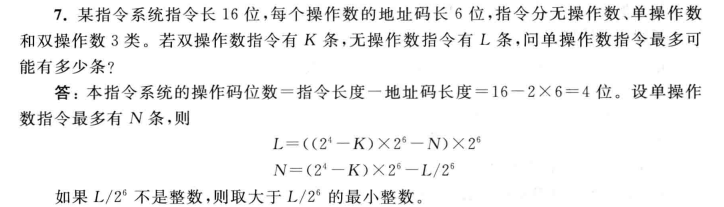

5.2.2 指令操作码的扩展技术

第 6 章 中央处理器

6.1 控制器

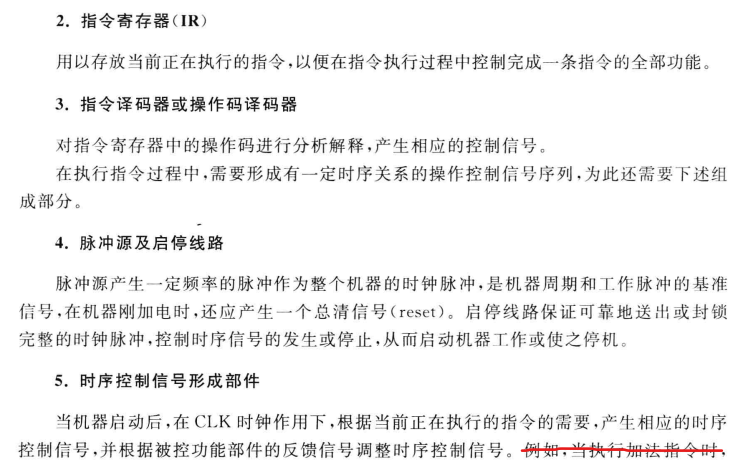

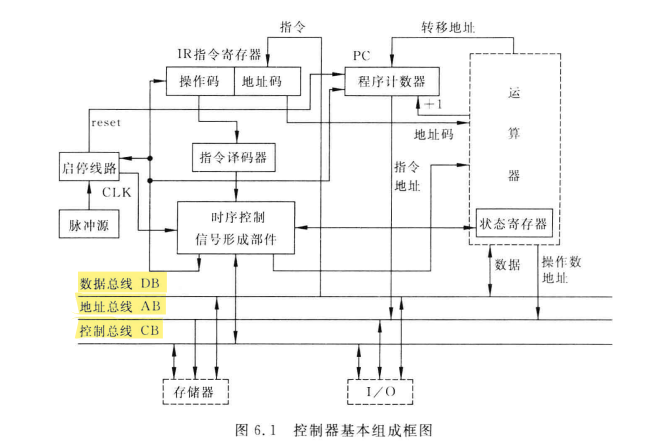

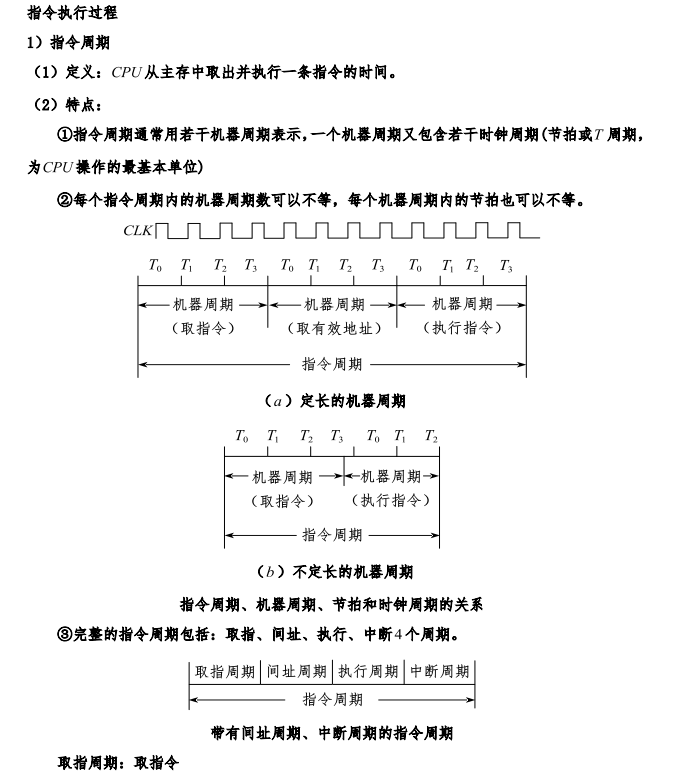

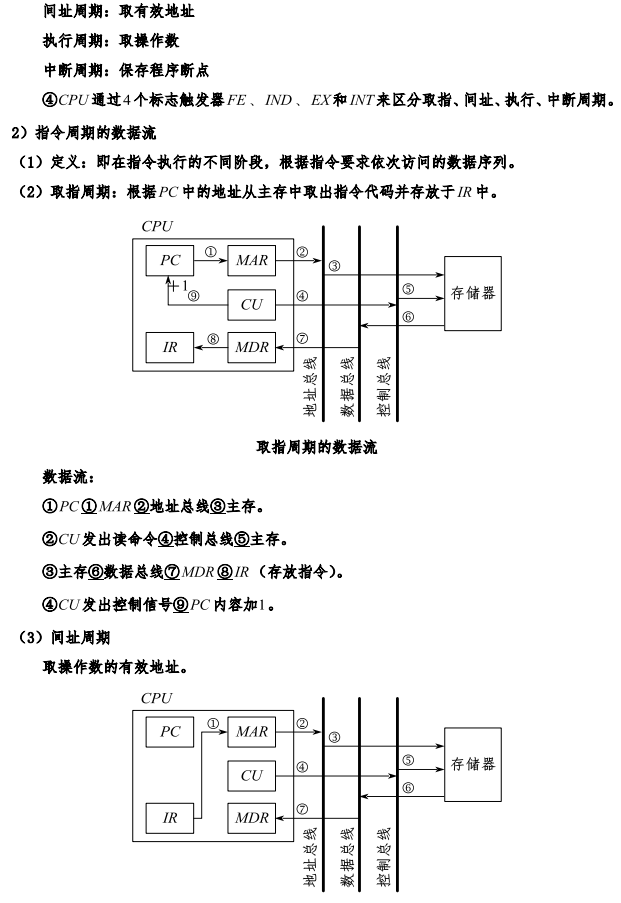

控制器的组成

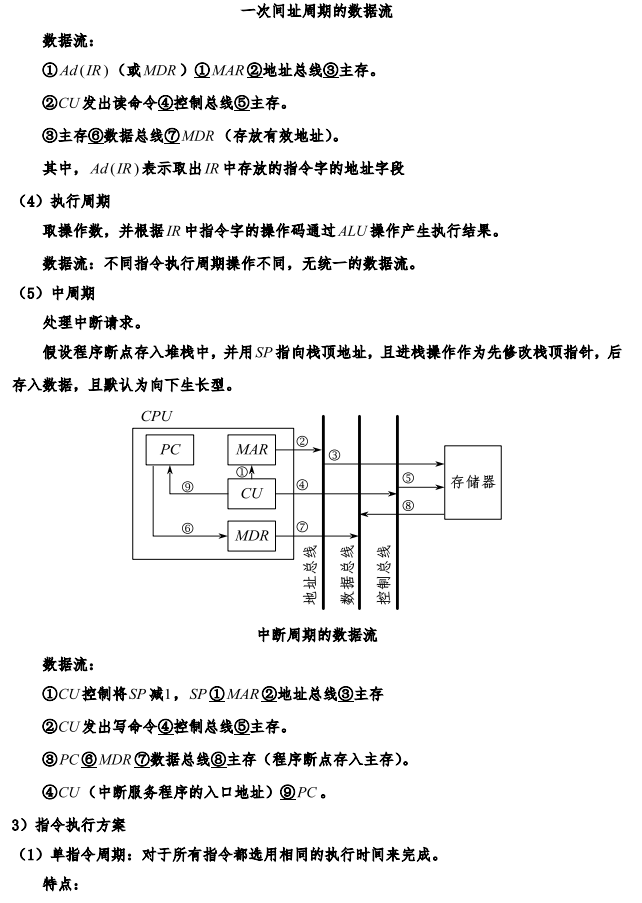

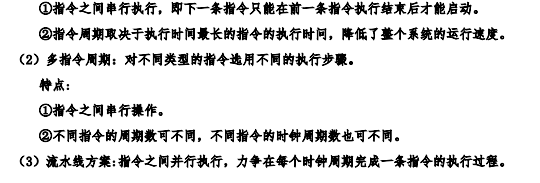

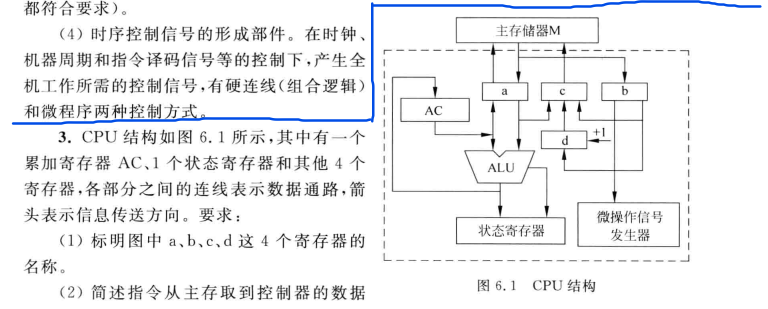

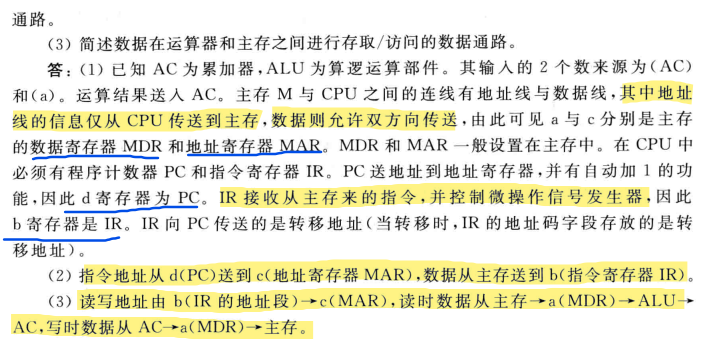

数据通路

题:数据通路

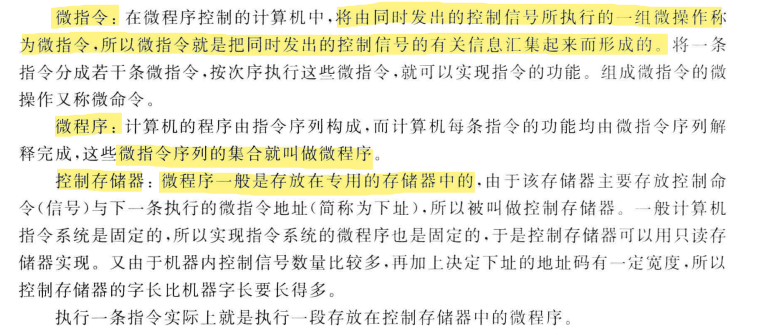

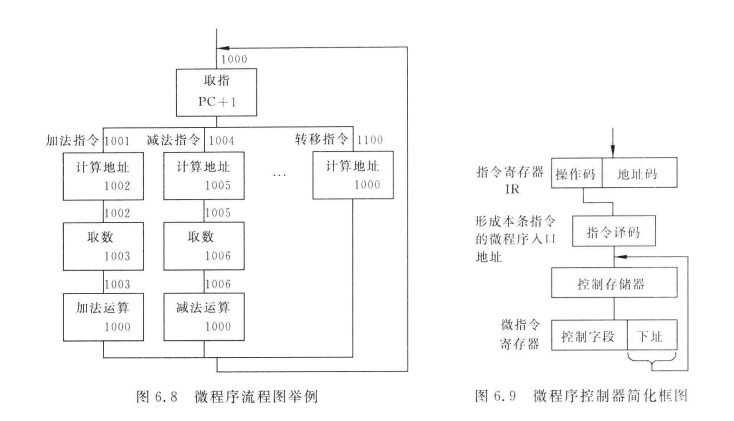

6.2 微程序

控存,控制存储器,ROM

6.3 微程序设计

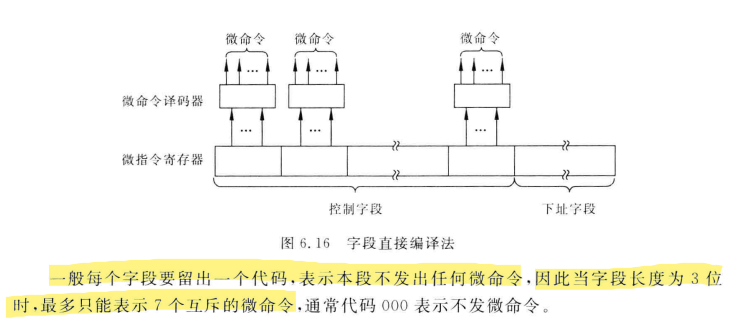

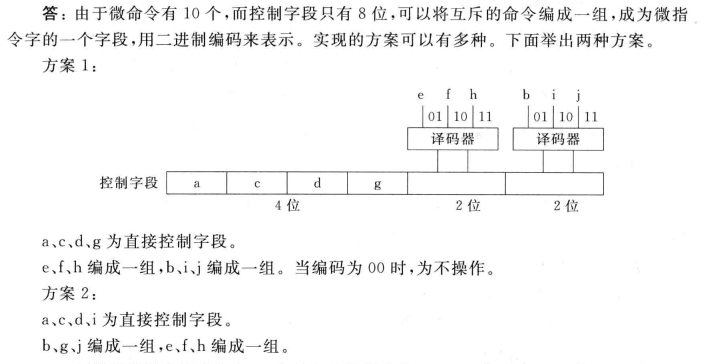

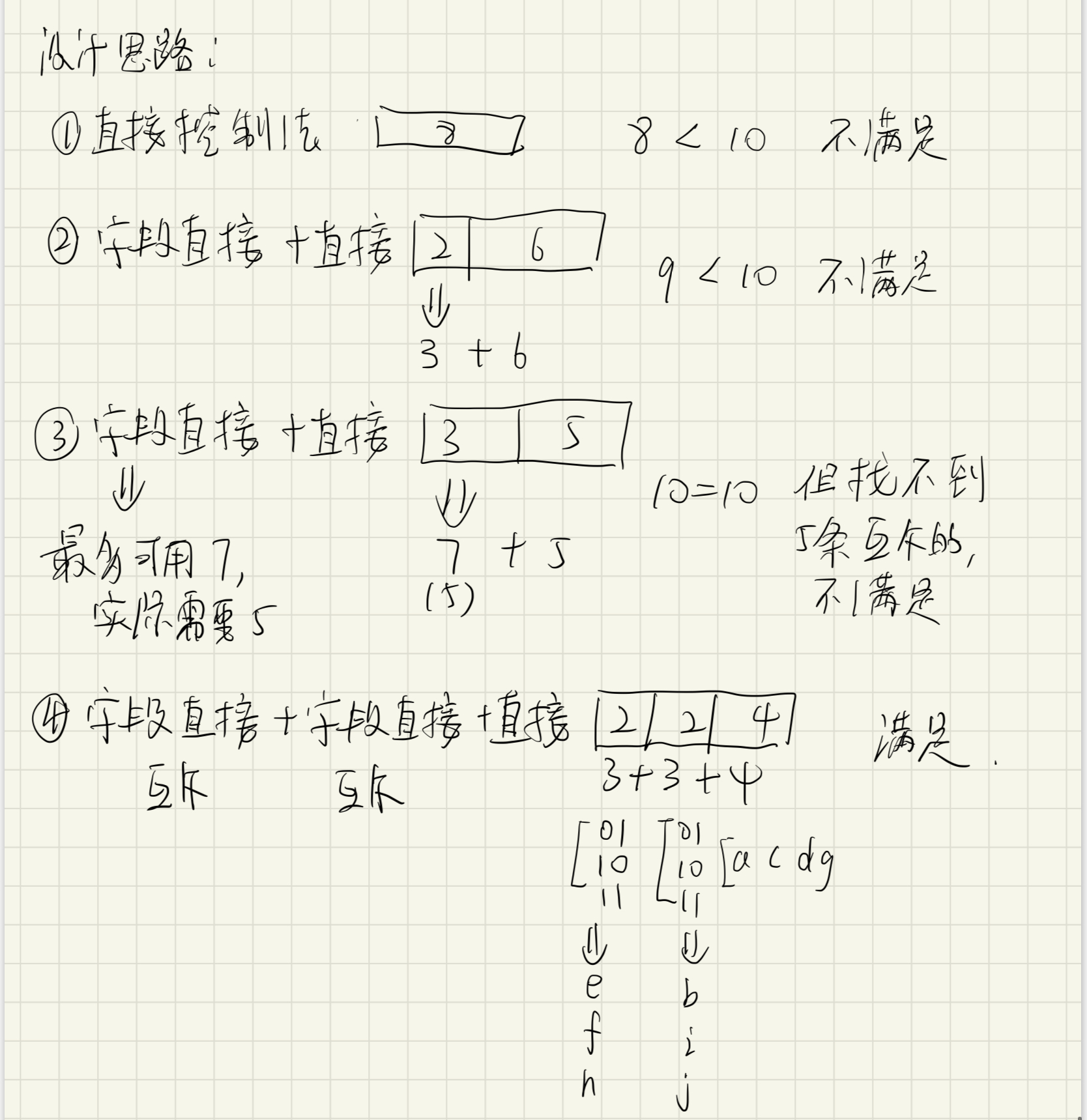

微程序控制字段的编译法

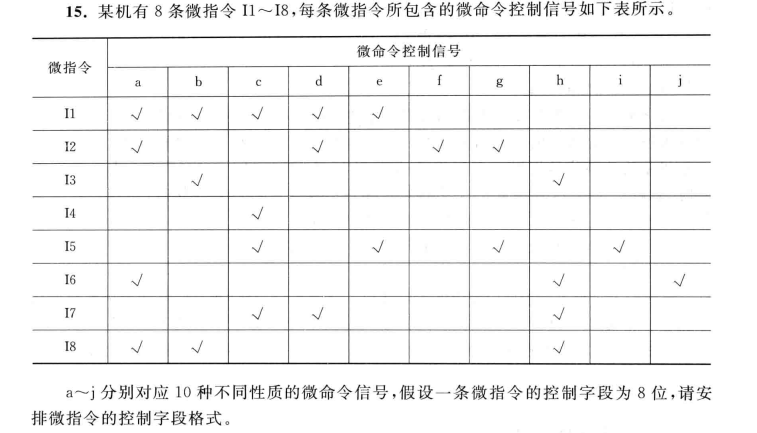

题:微指令控制字段格式设计

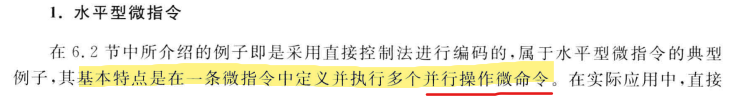

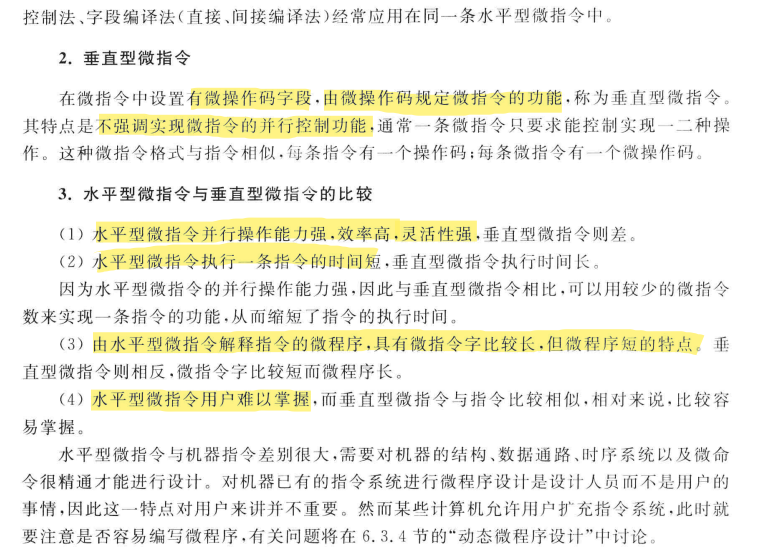

微指令格式

6.5 流水线

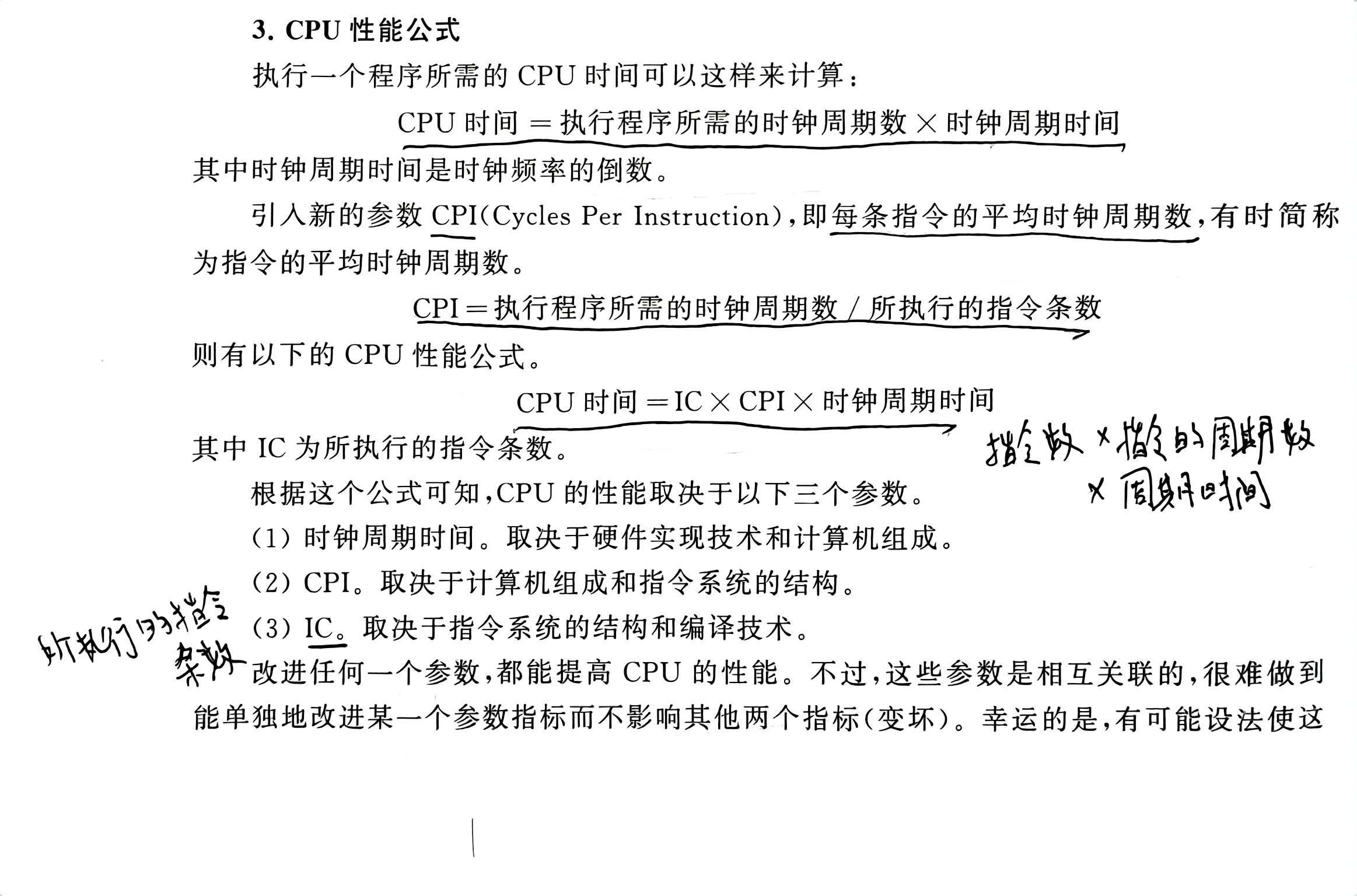

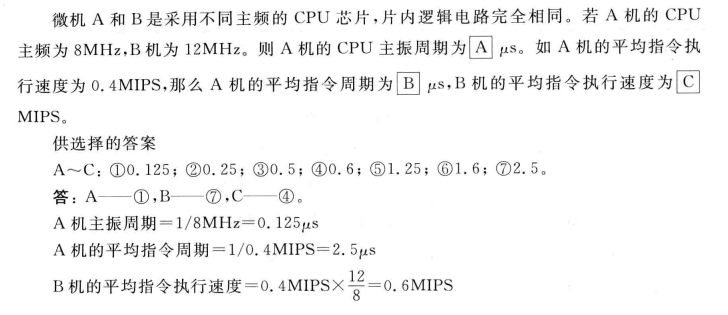

CPU 性能公式

题:CPU 性能

流水线阻塞

流水线阻塞是指在流水线处理器中,由于某些原因导致流水线暂停或减速,从而影响处理器性能。流水线阻塞的主要原因有数据相关、程序转移和中断请求。下面分别解释这三种情况及其解决方法:

- 数据相关(Data Dependency):

数据相关是指一个指令需要等待前一个或多个指令完成数据操作才能执行。这种情况下,流水线需要暂停,等待所需数据准备好。数据相关主要包括RAW(Read After Write,先写后读)、WAR(Write After Read,先读后写)和WAW(Write After Write,先写后写)。

解决方法:

- 指令调度:对指令进行重新排序,使得数据相关的指令之间有足够的间隔,以便在等待数据时处理其他指令。

- 数据前推(Data Forwarding):将上一级流水线段的计算结果直接传递给下一级流水线段,而不是等待寄存器更新。

- 寄存器重命名:通过使用更多的寄存器来消除WAW和WAR相关。

- 程序转移(Control Dependency):

程序转移是指流水线处理器遇到分支指令(如条件跳转、循环等)时,需要等待分支指令执行完毕才能确定下一条指令的地址。这会导致流水线暂停,等待新指令地址。

解决方法:

- 预测分支(Branch Prediction):通过硬件或软件预测分支的结果,提前获取下一条指令的地址,以减少等待时间。

- 延迟分支(Delayed Branching):将分支指令后面的无关指令(与分支无关)提前执行,以减少流水线暂停时间。

- 分支目标缓冲(Branch Target Buffer,BTB):缓存分支指令的目标地址,以加速分支指令的执行。

- 中断请求(Interrupt Request):

中断请求是指处理器在执行指令过程中收到外部或内部的中断信号,需要暂停当前任务,切换到中断服务程序。这会导致流水线暂停,等待中断处理完成。

解决方法:

- 中断屏蔽:在处理关键任务时,暂时屏蔽低优先级的中断请求,以减少流水线阻塞。

- 优先级设置:为不同类型的中断设置优先级,确保高优先级中断能够及时处理,降低流水线阻塞的影响。

- 硬件支持:使用硬件支持的中断处理机制,如嵌套中断向量表(Nested Interrupt Vector Table),加速中断处理过程,减少流水线阻塞时间。

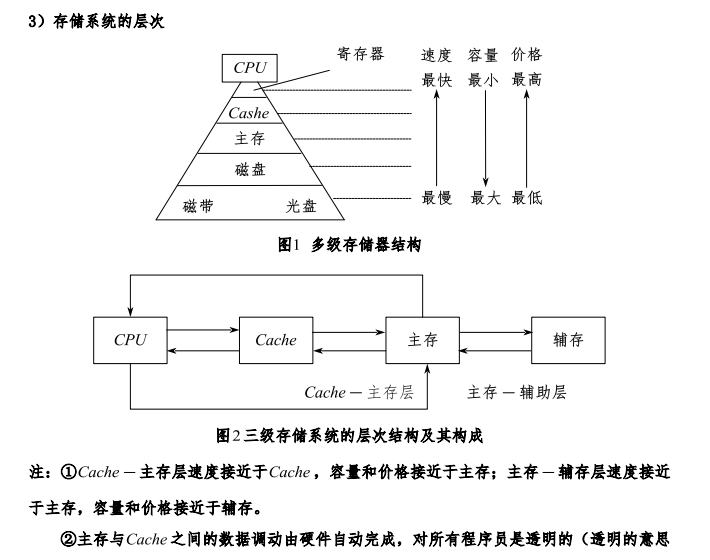

第 7 章 存储系统

7.1 存储系统的层次结构

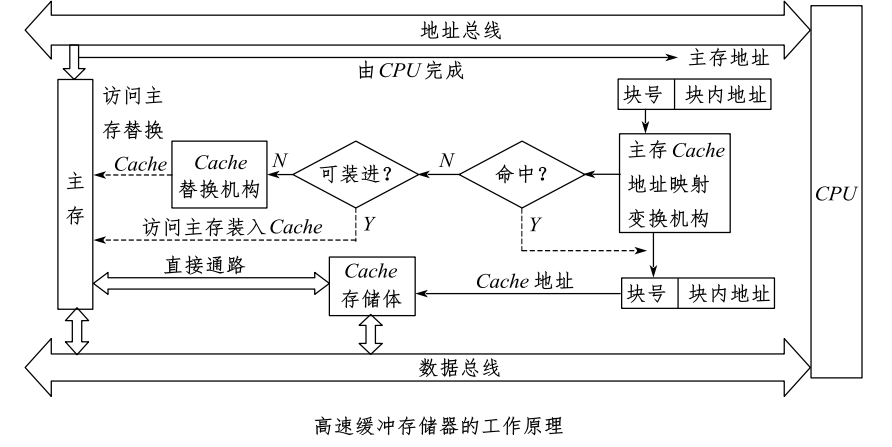

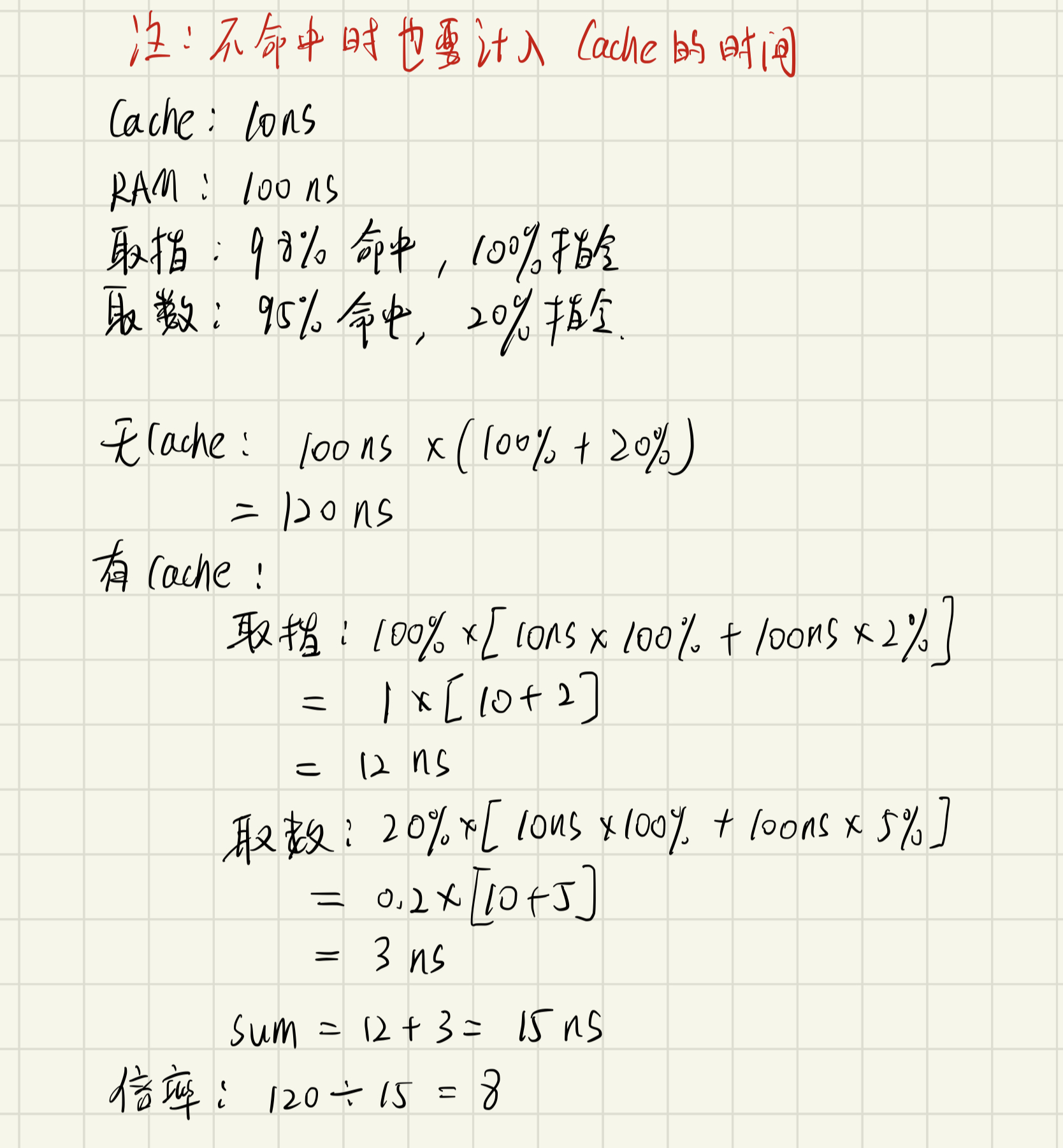

7.2 高速缓冲存储器 cache

cache 工作原理

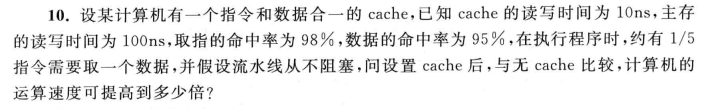

题:cache 命中率

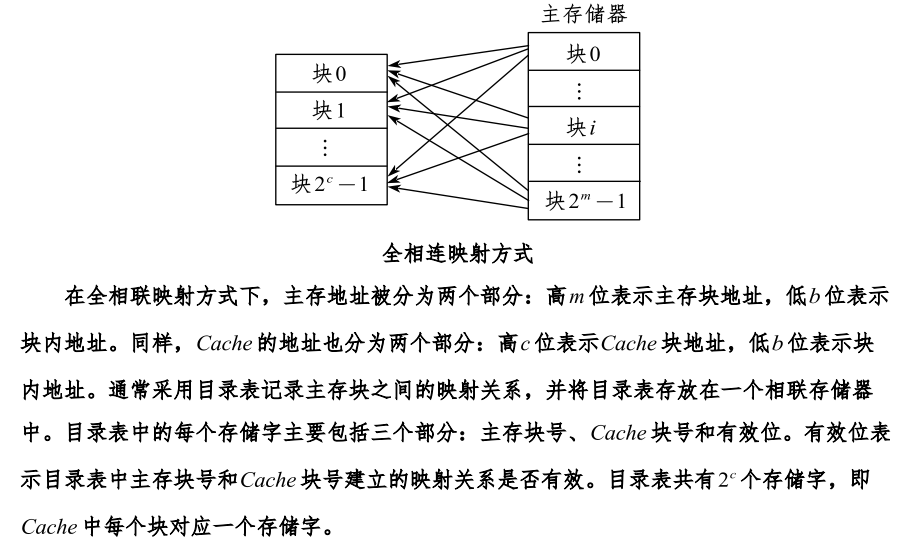

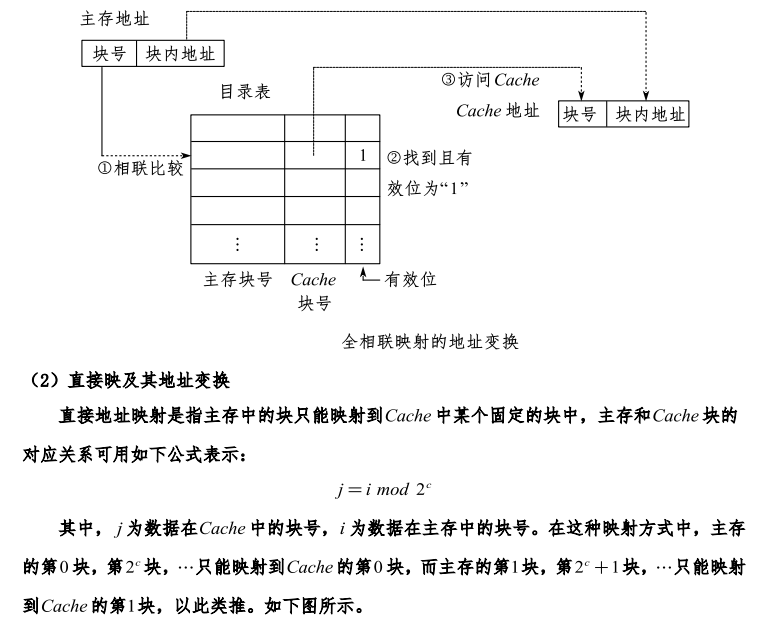

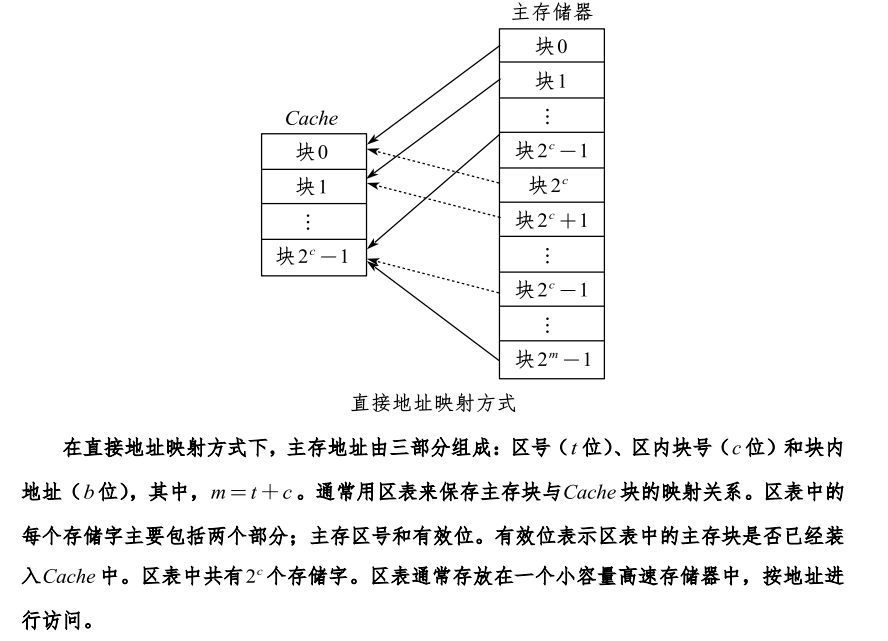

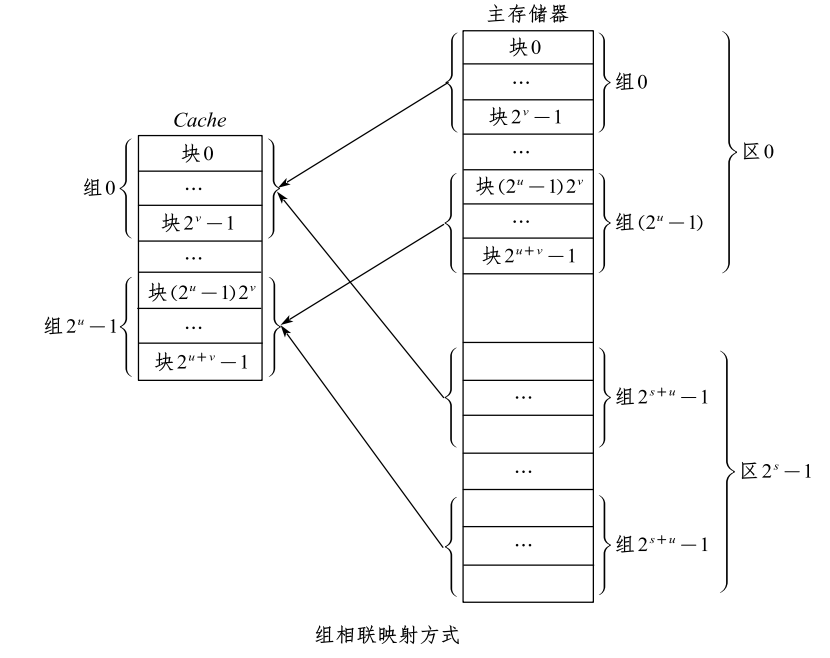

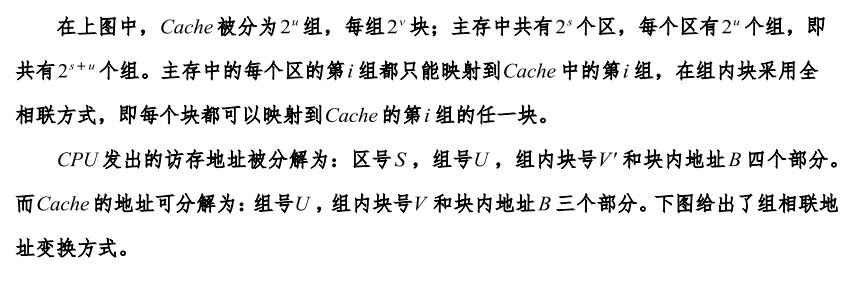

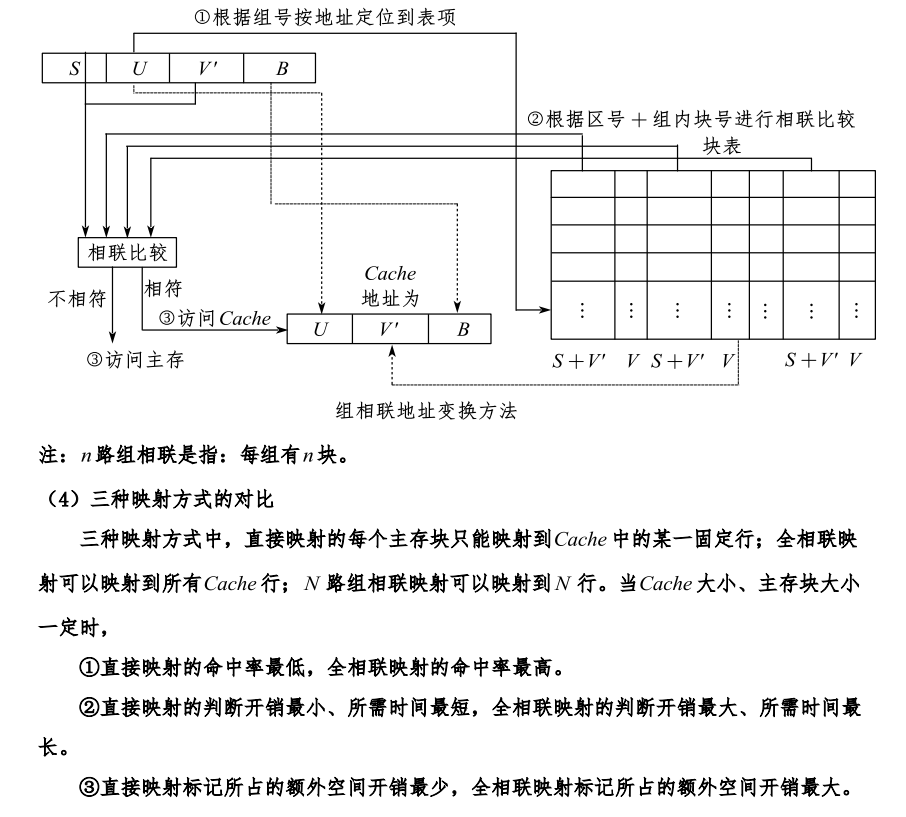

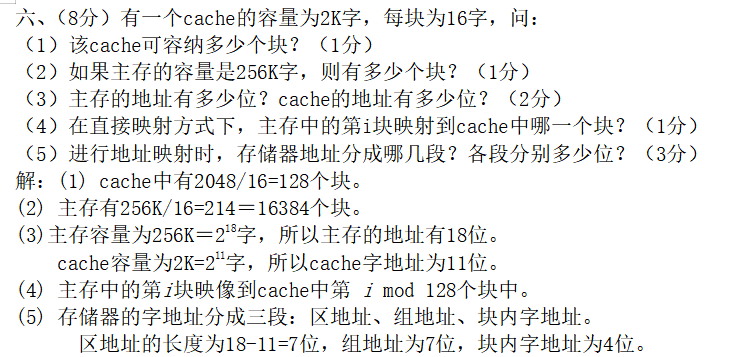

cache 地址映像

题:地址映像

注:存储块数 != 块数

区号:RAM地址位数 - cache地址位数

组号:cache总存储块数 / 块数

(块数:几路组相联就是几块数,一般为4;cache总存储块数 = cache总容量 / 一存储块的容量)

块号:log(块数),一般为2

块内地址:log(块的字数)

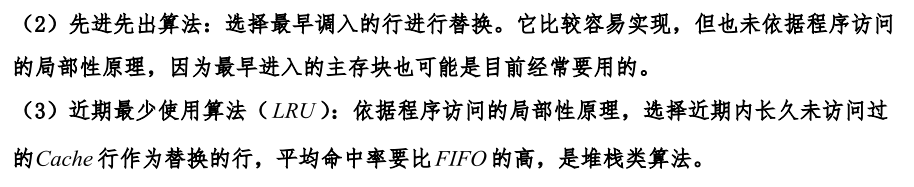

cache 替换算法

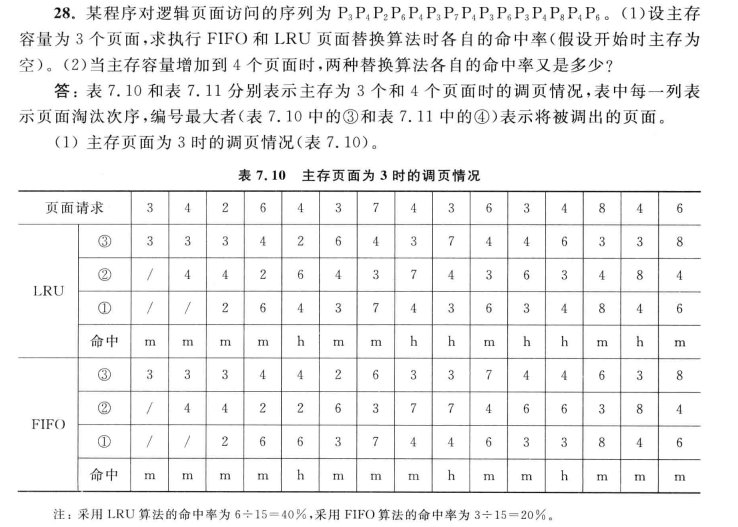

题:替换算法

m表示未命中,h表示命中

请求的页面从下往上顶掉最上方的页面,当请求的页面原本就在缓存中时视为命中。

LRU:命中时仍然执行不命中时的操作(请求的页面从下往上顶掉最上方的页面)

LRU:命中时把命中的块放到最下方,其他块顺次上移

FIFO:命中时不执行操作